### **MIDTERM EXAMINATION**

Spring 2009 CS302- Digital Logic Design (Session - 2)

| Question No: 1 (Marks: 1) - Please choose one                                                  |  |  |  |

|------------------------------------------------------------------------------------------------|--|--|--|

| The first Least Significant digit in decimal number system has                                 |  |  |  |

|                                                                                                |  |  |  |

| ▶ position 0 and weight equal to 1                                                             |  |  |  |

| ▶ position 1 and weight equal to 0                                                             |  |  |  |

| ▶ position 1 and weight equal to 10                                                            |  |  |  |

| ▶ position 0 and weight equal to 10                                                            |  |  |  |

| Question No: 2 (Marks: 1) - Please choose one                                                  |  |  |  |

| The decimal equivalent of the binary number "10011" is                                         |  |  |  |

|                                                                                                |  |  |  |

| <b>▶</b> 19                                                                                    |  |  |  |

| ▶ 99                                                                                           |  |  |  |

| <b>▶</b> 29                                                                                    |  |  |  |

| ► None of given options                                                                        |  |  |  |

|                                                                                                |  |  |  |

| Question No: 3 (Marks: 1) - Please choose one                                                  |  |  |  |

| The ANSI/IEEE Standard 754 defines aSingle-Precision Floating Point format for binary numbers. |  |  |  |

|                                                                                                |  |  |  |

| ► 8-bit                                                                                        |  |  |  |

| ► 16-bit                                                                                       |  |  |  |

| ► 32-bit                                                                                       |  |  |  |

► 64-bit

## Question No: 4 (Marks: 1) - Please choose one

The binary value "11011" is equivalent to \_\_\_\_\_

- **▶** 1B

- ▶ 1C

- ▶ 1D

- ▶ 1E

## **Question No: 5** (Marks: 1) - Please choose one

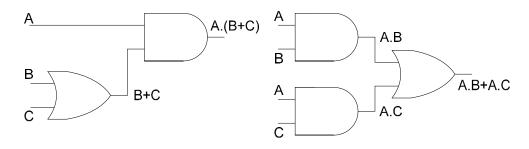

The circuit diagram given below explains \_\_\_\_\_

- ► Demorgan's Law

- ► Commutative Law

- ► Associative Law

- ▶ Distributive Law

## **Question No: 6** (Marks: 1) - Please choose one

The diagram given below represents \_\_\_\_\_

- ▶ Demorgans law

- ► Associative law

- ▶ Product of sum form

- ► Sum of product form

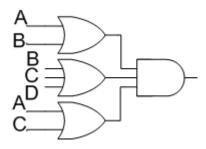

### **Question No: 7** (Marks: 1) - Please choose one

NOR gate is formed by connecting \_\_\_\_\_

- ▶ OR Gate and then NOT Gate

- ▶ NOT Gate and then OR Gate

- ► AND Gate and then OR Gate

- ▶ OR Gate and then AND Gate

## **Question No: 8** (Marks: 1) - Please choose one

"74ALS" stands for \_\_\_\_\_

- ► Advanced Low-frequency Schottky TTL

- Advanced Low-dissipation Schottky TTL

- ► Advanced Low-Power Schottky TTL

- ► Advanced Low-propagation Schottky TTL

Join: <a href="http://vumonster.ning.com">http://vumonster.ning.com</a> For Exclusive Projects, Reports & Latest Papers

| <b>Question No: 9</b>                                                            | ( Marks: 1 ) - Please choose one                       |  |  |  |

|----------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|

| An adder circuit of                                                              | can be used to perform subtraction operation           |  |  |  |

| ► True                                                                           |                                                        |  |  |  |

| ► False                                                                          |                                                        |  |  |  |

| Question No: 10                                                                  | ( Marks: 1 ) - Please choose one                       |  |  |  |

| For a 3-to-8 decoder how many 2-to-4 decoders will be required?                  |                                                        |  |  |  |

|                                                                                  |                                                        |  |  |  |

| <b>▶</b> 2                                                                       |                                                        |  |  |  |

| <b>▶</b> 3                                                                       |                                                        |  |  |  |

|                                                                                  |                                                        |  |  |  |

| <b>▶</b> 4                                                                       |                                                        |  |  |  |

| ▶ 1                                                                              |                                                        |  |  |  |

| Question No: 11                                                                  | ( Marks: 1 ) - Please choose one                       |  |  |  |

| 3-to-8 decoder can be used to implement Standard SOP and POS Boolean expressions |                                                        |  |  |  |

|                                                                                  |                                                        |  |  |  |

| ► True                                                                           |                                                        |  |  |  |

| ► False                                                                          |                                                        |  |  |  |

|                                                                                  |                                                        |  |  |  |

| <b>Question No: 12</b>                                                           | ( Marks: 1 ) - Please choose one                       |  |  |  |

| Two 2-input, 4-b multiplexer.                                                    | it multiplexers 74X157 can be connected to implement a |  |  |  |

|                                                                                  |                                                        |  |  |  |

| ► 2-input, 4-b                                                                   | it                                                     |  |  |  |

| ► 4-input, 8-b                                                                   | it                                                     |  |  |  |

► 4-input, 16-bit

| ► 2-input, 8-bi        | t                                                          |                                     |      |

|------------------------|------------------------------------------------------------|-------------------------------------|------|

| Question No: 13        | ( Marks: 1 ) - Please choose                               | e one                               |      |

|                        | of two 4-input multiplexers, co<br>ether through a 4-input | nnected to form a 16-input multiple | xer, |

| ► AND                  |                                                            |                                     |      |

| ► OR                   |                                                            |                                     |      |

| ► NAND                 |                                                            |                                     |      |

| ► XOR                  |                                                            |                                     |      |

| Question No: 14        | ( Marks: 1 ) - Please choose                               | e one                               |      |

| The Programmable array | e Array Logic (PAL) has                                    | AND array and a C                   | OR   |

| ► Fixed, progr         | ammable                                                    |                                     |      |

| ► Programmal           | ole, fixed                                                 |                                     |      |

| ► Fixed, fixed         |                                                            |                                     |      |

| ► Programmal           | ble, programmable                                          |                                     |      |

| Question No: 15        | ( Marks: 1 ) - Please choose                               | e one                               |      |

| Sequential circuits    | have storage elements                                      |                                     |      |

|                        |                                                            |                                     |      |

| ► True                 |                                                            |                                     |      |

| ► False                |                                                            |                                     |      |

Join: <a href="http://vumonster.ning.com">http://vumonster.ning.com</a> For Exclusive Projects, Reports & Latest Papers

### **Question No: 16** (Marks: 1) - Please choose one

Demultiplexer has

- ► Single input and single outputs.

- ► Multiple inputs and multiple outputs.

- ► Single input and multiple outputs.

- ▶ Multiple inputs and single output.

### Question No: 17 (Marks: 1)

How standard Boolean expressions can be converted into truth table format.

## Question No: 18 (Marks: 1)

$$(A + C).(C + D).(B + C + D)$$

State whether the above expression is SOP or POS?

### Question No: 19 (Marks: 2)

Draw 3 variable K-map table of boolean expression given below ABC+A'B'C

### Question No: 20 (Marks: 3)

Add -13 and +7 by converting them in binary system your result must be in binary.

#### Question No: 21 (Marks: 5)

Explain "OR" Gate and some of its uses

Question No: 22 (Marks: 10)

Explain NAND Gate, how it can be used to implement three basic gates

Join: http://vumonster.ning.com For Exclusive Projects, Reports & Latest Papers